# AZ12000, AZ12001

## **Phase-Locked Loop Clock Generator**

### **FEATURES**

- PECL (AZ12000) or LVDS (AZ12001) Outputs

- Operating Range 3.0V to 5.5V

- Internal Crystal Oscillator Driver

- Internal Edge-Matching Phase/Frequency Detector

- Internal Charge-Pump and Integrator Amplifier

- Internal or External VCO

- Divide by 4, 8, 16, 32

- RF Bipolar Design for Low Phase Noise

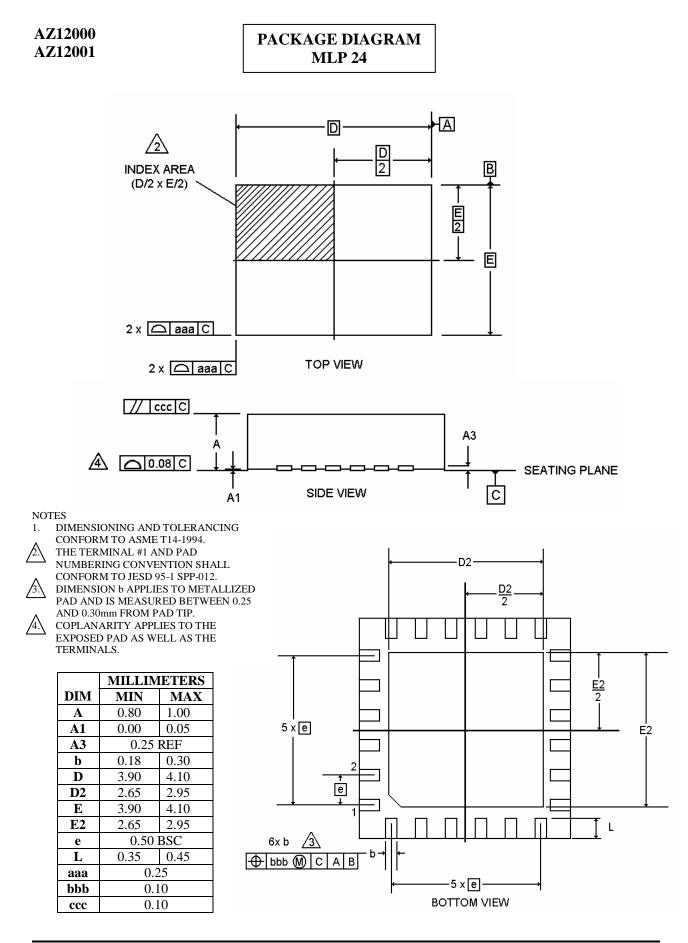

- Available in a 4x4mm MLP Package

# DESCRIPTION

#### PACKAGE AVAILABILITY

| PACKAGE              | PART NO.   | MARKING               | NOTES |

|----------------------|------------|-----------------------|-------|

| MLP 24 (4x4)         | AZ12000K   | AZ12000               | 1,2   |

|                      | 71212000IX | <date code=""></date> |       |

| <b>MID</b> $24(4.4)$ | AZ12001K   | AZ12001               | 1,2   |

| MLP 24 (4x4)         | AZ12001K   | <date code=""></date> |       |

| DIE                  | AZ12000XP  | N/A                   | 3     |

| DIE                  | AZ12001XP  | N/A                   | 3     |

1 Add R1 at end of part number for 7 inch (1K parts), R2 for 13 inch (2.5K parts) Tape & Reel.

2 Date code format: "YY" for year followed by "WW" for week.

3 Waffle Pack

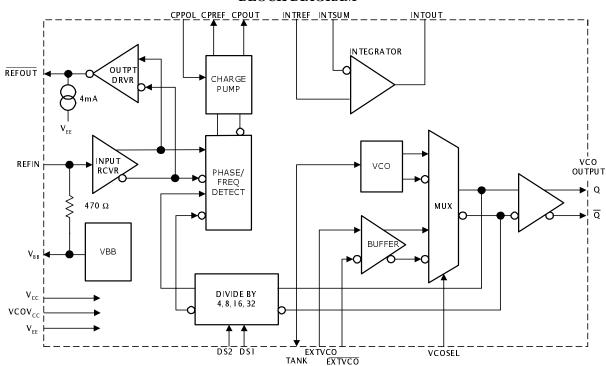

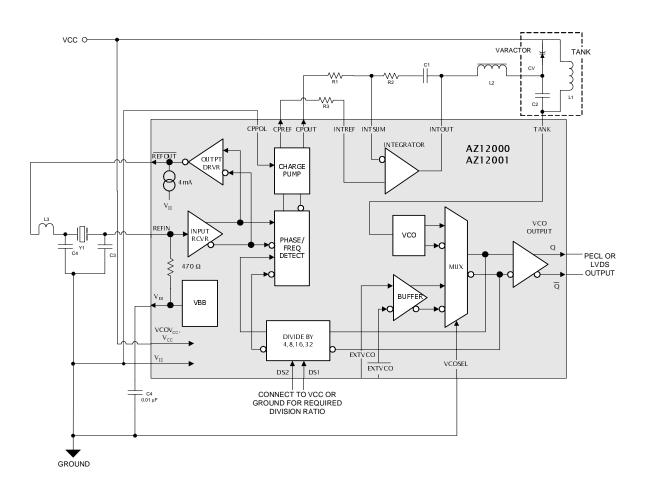

The AZ12000/AZ12001 contains all of the functional elements necessary to implement a Phase-Locked Loop for clock multiplication at frequencies up to 800 MHz. A reference crystal oscillator driver operates at frequencies up to 200 MHz providing support for 4 times multiplication. The dynamic properties of the PLL are under the control of the user through selection of the desired external components.

#### **BLOCK DIAGRAM**

Bottom Center pad may be left open or tied to  $V_{\mbox{\scriptsize EE}}.$

| Absolute Maximum | Ratings are those | values beyond | which device  | life may be impaired. |

|------------------|-------------------|---------------|---------------|-----------------------|

| Absolute Maximum | Ratings are those | values beyond | which ut vice | me may be impaired.   |

| Symbol           | Characteristic                                  | Rating      | Unit |

|------------------|-------------------------------------------------|-------------|------|

| V <sub>CC</sub>  | Power Supply $(V_{EE} = GND)$                   | 0 to +6.0   | Vdc  |

| VI               | Input Voltage $(V_{EE} = GND)$                  | 0 to +6.0   | Vdc  |

| I <sub>OUT</sub> | ECL/PECL Output Current — Continuous<br>— Surge | 40<br>80    | mA   |

| T <sub>A</sub>   | Operating Temperature Range                     | -40 to +85  | °C   |

| T <sub>STG</sub> | Storage Temperature Range                       | -65 to +150 | °C   |

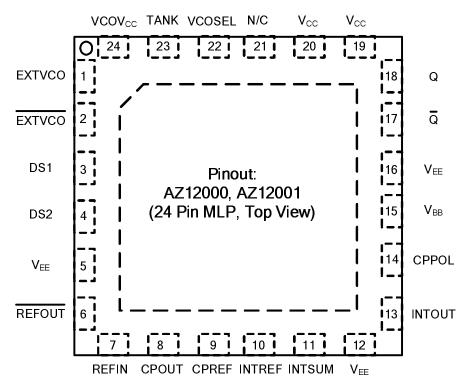

#### AZ12000 FUNCTIONAL PIN DESCRIPTIONS

| Pin No | Pin Name                              | Functional Description                                                                                                                                                       | Logic Level |

|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|        | REFIN                                 | <b>Reference Crystal Resonator Input</b> This pin includes an on-chip 470 $\Omega$ pull down resistor to V <sub>BB</sub> . The input from the resonator circuit should be AC |             |

|        |                                       | coupled.<br>Crystal Resonator Output Drive This pin is an inverted and amplified version                                                                                     |             |

|        |                                       | of the signal on the REFIN pin. The gain from REFIN to REFOUT is                                                                                                             |             |

|        | REFOUT                                | approximately 20. The IC includes a 4 ma on-chip current source. If more                                                                                                     | ECL/PECL    |

|        |                                       | current is needed, the REFOUT pin may be connected to $V_{\text{EE}}$ through a resistor                                                                                     |             |

|        |                                       | to provide up to 8 ma additional current.                                                                                                                                    |             |

|        |                                       | Charge Pump Reference Output The pin voltage is nominally 1.2 volts below                                                                                                    |             |

|        | CPREF                                 | $V_{CC}$ . If an external integrator is used, CPREF should be connected to the                                                                                               |             |

|        |                                       | integrator reference input through a bias current cancellation network.                                                                                                      |             |

|        |                                       | <b>Charge Pump Output</b> The charge pump output voltage is V(CPREF) ±0.3V                                                                                                   |             |

|        | CPOUT                                 | during a phase correction pulse. When there is no correction pulse the output                                                                                                |             |

|        |                                       | goes high impedance. If an external integrator is used, CPOUT should be                                                                                                      |             |

|        |                                       | connected to the input integrator resistor.                                                                                                                                  |             |

|        |                                       | <b>Charge Pump Polarity</b> Logic LOW on this pin causes CPOUT to go low when the VCO frequency is too low, and go high when the VCO frequency is                            |             |

|        |                                       | too high. Logic HIGH on this pin causes CPOUT to go low when the VCO                                                                                                         |             |

|        | CPPOL                                 | frequency is too high, and go high when the VCO frequency is too low. This                                                                                                   | CMOS/TTL    |

|        | CITOL                                 | pin should be LOW when the internal VCO is used.                                                                                                                             | compatible  |

|        |                                       |                                                                                                                                                                              |             |

|        |                                       | If this pin is left open it is pulled to the HIGH condition.                                                                                                                 |             |

|        | INTER                                 | Integrator Reference Input This pin should be connected to CPREF through a                                                                                                   |             |

|        | INTREF                                | bias current cancellation network                                                                                                                                            |             |

|        | INTSUM                                | Integrator Summing Junction This pin is the summing junction for the                                                                                                         |             |

|        |                                       | integrator amplifier                                                                                                                                                         |             |

|        | INTOUT                                | Integrator Output                                                                                                                                                            |             |

|        |                                       | Internal/External VCO Select Logic HIGH on this pin enables the internal                                                                                                     |             |

|        | VCOCEI                                | VCO. Logic LOW on this pin disables the internal VCO and allows use of the                                                                                                   | CMOS/TTL    |

|        | VCOSEL                                | EXTVCO inputs.                                                                                                                                                               | compatible  |

|        |                                       | If this pin is left open it is pulled to the HIGH condition.                                                                                                                 |             |

|        | TANK                                  | <b>VCO Tank</b> The tank components connect between this pin and $V_{CC}$ .                                                                                                  |             |

|        | EXTVCO                                | <b>External VCO Input</b> The external VCO input pins should be driven                                                                                                       |             |

|        | EXTVCO                                | differentially for best performance.                                                                                                                                         | ECL/PECL    |

|        |                                       | <b>Divide Select</b> VCO divide ratios are selected as shown:                                                                                                                |             |

|        |                                       |                                                                                                                                                                              |             |

|        |                                       | DS2 DS1 Ratio                                                                                                                                                                |             |

|        | DS2                                   | LOW LOW ÷4                                                                                                                                                                   | CMOS/TTL    |

|        | DS1                                   | LOW HIGH ÷8                                                                                                                                                                  | compatible  |

|        |                                       | HIGH LOW ÷16                                                                                                                                                                 |             |

|        |                                       | HIGH HIGH ÷32                                                                                                                                                                |             |

|        |                                       | If the pins are left open they are pulled to the HIGH condition.                                                                                                             |             |

|        | Q                                     | Clock Output These pins are the main (multiplied) clock output.                                                                                                              | ECL/PECL    |

|        | Q<br>N/C                              | No Connect This nin is used during featers text. It must be left error                                                                                                       |             |

|        | IN/C                                  | No Connect This pin is used during factory test. It mist be left open.<br>Reference Voltage Output This pin is used to bias the REFIN signal. It must                        |             |

|        | $V_{BB}$                              |                                                                                                                                                                              |             |

|        | V                                     | be bypassed externally to the VEE pins with a 0.01 μF capacitor.<br><b>Positive Supply</b> +3.0 to +5.5 V for PECL mode, Ground for ECL mode.                                |             |

|        | V <sub>CC</sub><br>VCOV <sub>CC</sub> | <b>VCO Positive Supply</b> +3.0 to +5.5 V for PECL mode, Ground for ECL mode.                                                                                                |             |

|        |                                       | Negative Supply Ground for PECL mode, -3.0 to -5.5 V for ECL mode.                                                                                                           |             |

|        | $V_{EE}$                              | regauve Supply Ground for PECL mode, -3.0 to -5.5 V for ECL mode.                                                                                                            |             |

#### AZ12001 FUNCTIONAL PIN DESCRIPTIONS

| Pin No | Pin Name           | Functional Description                                                                | Logic Level |

|--------|--------------------|---------------------------------------------------------------------------------------|-------------|

|        |                    | <b>Reference Crystal Resonator Input</b> This pin includes an on-chip 470 Ω pull      | ~           |

|        | REFIN              | down resistor to $V_{BB}$ . The input from the resonator circuit should be AC         |             |

|        |                    | coupled.                                                                              |             |

|        |                    | Crystal Resonator Output Drive This pin is an inverted and amplified version          |             |

|        |                    | of the signal on the REFIN pin. The gain from REFIN to REFOUT is                      |             |

|        | REFOUT             | approximately 20. The IC includes a 4 ma on-chip current source. If more              | PECL        |

|        |                    | current is needed, the REFOUT pin may be connected to $V_{EE}$ through a resistor     |             |

|        |                    | to provide up to 8 ma additional current.                                             |             |

|        |                    | Charge Pump Reference Output The pin voltage is nominally 1.2 volts below             |             |

|        | CPREF              | V <sub>CC</sub> . If an external integrator is used, CPREF should be connected to the |             |

|        |                    | integrator reference input through a bias current cancellation network.               |             |

|        |                    | <b>Charge Pump Output</b> The charge pump output voltage is V(CPREF) ±0.3V            |             |

|        | CPOUT              | during a phase correction pulse. When there is no correction pulse the output         |             |

|        | CPUUI              | goes high impedance. If an external integrator is used, CPOUT should be               |             |

|        |                    | connected to the input integrator resistor.                                           |             |

|        |                    | Charge Pump Polarity Logic LOW on this pin causes CPOUT to go low                     |             |

|        |                    | when the VCO frequency is too low, and go high when the VCO frequency is              |             |

|        |                    | too high. Logic HIGH on this pin causes CPOUT to go low when the VCO                  | CMOS/TTL    |

|        | CPPOL              | frequency is too high, and go high when the VCO frequency is too low. This            | compatible  |

|        |                    | pin should be LOW when the internal VCO is used.                                      | compatible  |

|        |                    |                                                                                       |             |

|        |                    | If this pin is left open it is pulled to the HIGH condition.                          |             |

|        | INTREF             | Integrator Reference Input This pin should be connected to CPREF through a            |             |

|        | nunce              | bias current cancellation network                                                     |             |

|        | INTSUM             | Integrator Summing Junction This pin is the summing junction for the                  |             |

|        |                    | integrator amplifier                                                                  |             |

|        | INTOUT             | Integrator Output                                                                     |             |

|        |                    | Internal/External VCO Select Logic HIGH on this pin enables the internal              |             |

|        |                    | VCO. Logic LOW on this pin disables the internal VCO and allows use of the            | CMOS/TTL    |

|        | VCOSEL             | EXTVCO inputs.                                                                        | compatible  |

|        |                    |                                                                                       | eompariore  |

|        | THAN WE            | If this pin is left open it is pulled to the HIGH condition.                          |             |

|        | TANK               | <b>VCO Tank</b> The tank components connect between this pin and $V_{CC}$ .           |             |

|        | EXTVCO             | <b>External VCO Input</b> The external VCO input pins should be driven                | PECL        |

|        | EXTVCO             | differentially for best performance.                                                  |             |

|        |                    | <b>Divide Select</b> VCO divide ratios are selected as shown:                         |             |

|        |                    |                                                                                       |             |

|        | DGO                | DS2 DS1 Ratio                                                                         |             |

|        | DS2                | LOW LOW ÷4                                                                            | CMOS/TTL    |

|        | DS1                | LOW HIGH +8                                                                           | Compatible  |

|        |                    | HIGH LOW ÷16                                                                          |             |

|        |                    | HIGH HIGH ÷32                                                                         |             |

|        |                    | If the pins are left open they are pulled to the HIGH condition.                      |             |

|        | Q                  | Clock Output These pins are the main (multiplied) clock output.                       | LVDS        |

|        | Q                  | No Connect This pip is used during for the state of It (1, 1, 6)                      |             |

|        | N/C                | <b>No Connect</b> This pin is used during factory test. It must be left open.         |             |

|        | $V_{BB}$           | <b>Reference Voltage Output</b> This pin is used to bias the REFIN signal. It must    |             |

|        |                    | be bypassed externally to the VEE pins with a 0.01 $\mu$ F capacitor.                 |             |

|        | V <sub>CC</sub>    | Positive Supply +3.0 to +5.5 V                                                        |             |

|        | VCOV <sub>CC</sub> | VCO Positive Supply +3.0 to +5.5 V                                                    |             |

|        | V <sub>EE</sub>    | Negative Supply Ground                                                                |             |

| Symbol                | Characteristic                                                   | -40                      | )°C                      | 0°C                      |                          | 25°C                     |                          |                          | 85                       | Unit                     |      |

|-----------------------|------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------|

| Symbol                | Characteristic                                                   | Min                      | Max                      | Min                      | Max                      | Min                      | Тур                      | Max                      | Min                      | Max                      | Unit |

| $V_{BB}$              | Reference Voltage                                                | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.31 | V <sub>CC</sub><br>-1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V    |

| R <sub>PD</sub>       | REFIN Pull-Down resistor to $V_{BB}$                             |                          |                          |                          |                          |                          | 470                      |                          |                          |                          | Ω    |

| I <sub>CS</sub>       | REFOUT Current Source                                            |                          |                          |                          |                          |                          | 4.0                      |                          |                          |                          | ma   |

| V <sub>HCTL</sub>     | High level integrator output                                     |                          |                          |                          |                          | V <sub>CC</sub><br>-1.0  |                          |                          |                          |                          | V    |

| V <sub>LCTL</sub>     | Low level integrator output                                      |                          |                          |                          |                          |                          |                          | V <sub>EE</sub><br>+0.5  |                          |                          | V    |

| V <sub>OH</sub>       | Output HIGH Voltage <sup>1</sup><br>Q<br>Q                       | V <sub>CC</sub><br>-1085 | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1025 | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1025 | V <sub>CC</sub><br>-955  | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1025 | V <sub>CC</sub><br>-880  | mV   |

| V <sub>OL</sub>       | Output LOW Voltage <sup>1</sup><br>Q<br>Q                        | V <sub>CC</sub><br>-1830 | V <sub>CC</sub><br>-1555 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1620 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1705 | V <sub>CC</sub><br>-1620 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1620 | mV   |

| V <sub>IH</sub>       | Input HIGH Voltage,<br>PECL/ECL<br>EXTVCO<br>EXTVCO              | V <sub>CC</sub><br>-1165 | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1165 | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1165 |                          | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1165 | V <sub>CC</sub><br>-880  | mV   |

| V <sub>IL</sub>       | Input LOW Voltage,<br>PECL/ECL<br>EXTVCO<br>EXTVCO               | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1475 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1475 | V <sub>CC</sub><br>-1810 |                          | V <sub>CC</sub><br>-1475 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1475 | mV   |

| V <sub>IH</sub>       | Input HIGH Voltage,<br>TTL/CMOS<br>CPPOL<br>VCOSEL<br>DS2<br>DS1 | V <sub>EE</sub><br>+2.0  |                          | V <sub>EE</sub><br>+2.0  |                          | V <sub>EE</sub><br>+2.0  |                          |                          | V <sub>EE</sub><br>+2.0  |                          | V    |

| V <sub>IL</sub>       | Input HIGH Voltage,<br>TTL/CMOS<br>CPPOL<br>VCOSEL<br>DS2<br>DS1 |                          | V <sub>EE</sub><br>+0.8  |                          | V <sub>EE</sub><br>+0.8  |                          |                          | V <sub>EE</sub><br>+0.8  |                          | V <sub>EE</sub><br>+0.8  | V    |

| $I_{CC}$ ( $I_{EE}$ ) | Power Supply Current                                             |                          | 55                       |                          | 58                       |                          | 45                       | 58                       |                          | 60                       | mA   |

#### AZ12000 (PECL OUTPUT) DC CHARACTERISTICS ( $V_{CC} = +3.0$ to +5.5 V, $V_{EE} = GND$ )

1. Load is  $50\Omega$  to V<sub>CC</sub>-2V

### AZ12001 (LVDS OUTPUT) DC CHARACTERISTICS ( $V_{CC} = +3.0$ to +5.5 V, $V_{EE} = GND$ )

| C-makel                                | Changeteristic                                                   | -40°C                    |                          | 0°                       | C                        |                          | 25°C                     |                          | 85                       | T Inc. 4                 |      |

|----------------------------------------|------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------|

| Symbol                                 | Characteristic                                                   | Min                      | Max                      | Min                      | Max                      | Min                      | Тур                      | Max                      | Min                      | Max                      | Unit |

| V <sub>BB</sub>                        | Reference Voltage                                                | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.31 | V <sub>CC</sub><br>-1.26 | V <sub>CC</sub><br>-1.38 | V <sub>CC</sub><br>-1.26 | V    |

| R <sub>PD</sub>                        | REFIN Pull-Down resistor to $V_{BB}$                             |                          |                          |                          |                          |                          | 470                      |                          |                          |                          | Ω    |

| I <sub>CS</sub>                        | REFOUT Current Source                                            |                          |                          |                          |                          |                          | 4.0                      |                          |                          |                          | ma   |

| V <sub>HCTL</sub>                      | High level integrator output                                     |                          |                          |                          |                          | V <sub>CC</sub><br>-1.0  |                          |                          |                          |                          | V    |

| V <sub>LCTL</sub>                      | Low level integrator output                                      |                          |                          |                          |                          |                          |                          | V <sub>EE</sub><br>+0.5  |                          |                          | V    |

| V <sub>OH</sub>                        | Output HIGH Voltage <sup>1</sup><br>Q<br>Q                       |                          |                          |                          |                          |                          |                          |                          |                          |                          | mV   |

| V <sub>OL</sub>                        | Output LOW Voltage <sup>1</sup><br>Q<br>Q                        |                          |                          |                          |                          |                          |                          |                          |                          |                          | mV   |

| V <sub>IH</sub>                        | Input HIGH Voltage,<br>PECL/ECL<br>EXTVCO<br>EXTVCO              | V <sub>CC</sub><br>-1165 | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1165 | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1165 |                          | V <sub>CC</sub><br>-880  | V <sub>CC</sub><br>-1165 | V <sub>CC</sub><br>-880  | mV   |

| V <sub>IL</sub>                        | Input LOW Voltage,<br>PECL/ECL<br>EXTVCO<br>EXTVCO               | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1475 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1475 | V <sub>CC</sub><br>-1810 |                          | V <sub>CC</sub><br>-1475 | V <sub>CC</sub><br>-1810 | V <sub>CC</sub><br>-1475 | mV   |

| V <sub>IH</sub>                        | Input HIGH Voltage,<br>TTL/CMOS<br>CPPOL<br>VCOSEL<br>DS2<br>DS1 | V <sub>EE</sub><br>+2.0  |                          | V <sub>EE</sub><br>+2.0  |                          | V <sub>EE</sub><br>+2.0  |                          |                          | V <sub>EE</sub><br>+2.0  |                          | V    |

| V <sub>IL</sub>                        | Input HIGH Voltage,<br>TTL/CMOS<br>CPPOL<br>VCOSEL<br>DS2<br>DS1 |                          | V <sub>EE</sub><br>+0.8  |                          | V <sub>EE</sub><br>+0.8  |                          |                          | V <sub>EE</sub><br>+0.8  |                          | V <sub>EE</sub><br>+0.8  | V    |

| $I_{\rm CC} \left( I_{\rm EE} \right)$ | Power Supply Current                                             |                          |                          |                          | 60                       | İ                        |                          | 60                       |                          | 60                       | mA   |

1.  $100 \Omega$  between outputs

### AZ 12000 (PECL OUTPUT) AC CHARACTERISTICS ( $V_{CC} = +3.0$ to +5.5 V, $V_{EE} = GND$ )

| Symbol                    | Characteristic                                 | -40°C |     |     | 25°C |            |     |     | Unit |     |           |

|---------------------------|------------------------------------------------|-------|-----|-----|------|------------|-----|-----|------|-----|-----------|

|                           | Characteristic                                 | Min   | Тур | Max | Min  | Тур        | Max | Min | Тур  | Max | Oint      |

| A <sub>V1</sub>           | Gain, REFIN to REFOUT                          |       |     |     |      | 20         |     |     |      |     | V/V       |

| Zo                        | Output Impedance,<br>REFOUT                    |       |     |     |      | TBD        |     |     |      |     | Ω         |

| A <sub>PD</sub>           | Phase Detector Gain                            |       |     |     |      | 20.3       |     |     |      |     | radians/V |

| $\mathbf{f}_{\text{VCO}}$ | VCO frequency (Internal<br>or External)        |       |     |     |      |            | 800 |     |      |     | MHz       |

| $t_r / t_f$               | Output Rise & Fall Times<br>(20% - 80%) Q<br>Q |       |     |     |      | 120<br>120 |     |     |      |     | ps        |

### AZ12001 (LVDS OUTPUT) AC CHARACTERISTICS ( $V_{CC} = +3.0$ to +5.5 V, $V_{EE} = GND$ )

| Symbol                    | Characteristic                                 | -40°C |     |     | 25°C |      |     |     |     | Unit |           |

|---------------------------|------------------------------------------------|-------|-----|-----|------|------|-----|-----|-----|------|-----------|

|                           | Chai acteristic                                | Min   | Тур | Max | Min  | Тур  | Max | Min | Тур | Max  | Umt       |

| A <sub>V1</sub>           | Gain, REFIN to REFOUT                          |       |     |     |      | 20   |     |     |     |      | V/V       |

| Zo                        | Output Impedance,<br>REFOUT                    |       |     |     |      | TBD  |     |     |     |      | Ω         |

| A <sub>PD</sub>           | Phase Detector Gain                            |       |     |     |      | 20.3 |     |     |     |      | Radians/V |

| $\mathbf{f}_{\text{VCO}}$ | VCO frequency (Internal or External)           |       |     |     |      |      | 800 |     |     |      | MHz       |

| $t_r / t_f$               | Output Rise & Fall Times<br>(20% - 80%) Q<br>Q |       |     |     |      |      |     |     |     |      | ps        |

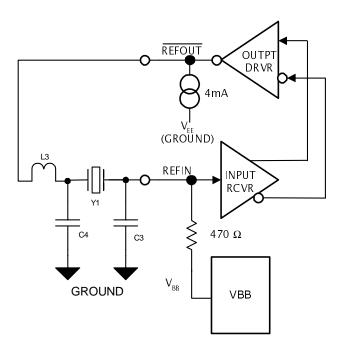

#### Internal Reference Oscillator

The PLL reference can be generated either with an internal oscillator or with an external source. In either case, the input is the REFIN pin. This should be AC coupled since the input is internally biased to  $V_{BB}$ . The REFOUT pin should be left open when an external reference is used.

The exact topology of the crystal circuit will vary based on the resonant mode of the crystal. The circuit shown is for a series resonant crystal. The AC gain between the REFIN and REFOUT pins is approximately 20. This value is sufficient to overcome crystal matching network losses without phase noise degradation caused by an excessive drive level. An internal current source on REFOUT eliminates the need for an external load resistor.

Figure 1 Reference Oscillator

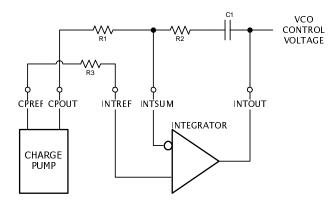

#### Loop Filter Design

The combination of the phase detector, amplifier, VCO and divider form a second-order phase-locked loop. Proper selection of the loop components is important to obtain stable, low jitter operation.

The loop bandwidth (or natural frequency,  $\omega_n$ ) and damping factor ( $\zeta$ ) are the two major driving forces that define the loop's response to a disturbance. The value of  $\zeta$  is typically 0.7 to ensure the fastest step response consistent with no ringing. However in many oscillator application  $\zeta$  may be 3 or higher to provide further phase noise reduction.  $\omega_n$  is chosen as a compromise between settling time, VCO jitter and reference feedthrough. These values can be computed by the following equations:

$$\omega_n = \frac{1}{N} \sqrt{\frac{K_{\phi} K_{VCO}}{\tau_1}}$$

$$\zeta = \frac{\tau_2 \omega_n}{2}$$

$$\tau_1 = R_1 C_1$$

$$\tau_2 = R_2 C_1$$

$K_{\phi}$  = Phase Detector Gain (20.3 radians/V)

$K_{VCO}$  = VCO Gain (radians/sec/volt)

N = Frequency Divisor value (4,8, 16 or 32)

The component definitions are shown in the figure below. R3 should be equal to R1 to minimize integrator offsets.

Figure 2 Charge Pump and Integrator

#### **Internal VCO**

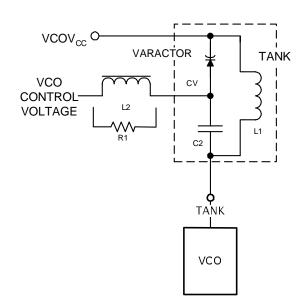

The internal VCO is designed for reliable, low jitter operation up to 800 MHz. It operates as a single terminal negative impedance type circuit.

The tank circuit should have a minimum Q of 12 for reliable operation. The series combination of CV and C1 resonate with L1 to set the operating frequency. The VCO control voltage is isolated through an inductor or resistor and changes the varactor capacitance based on that control voltage. Note that the CPPOL pin should be tied high for internal VCO operation since the tank frequency decreases with increasing control voltage.

Figure 3 Internal VCO with Tank

#### External VCO

When VCOSEL is high, the internal VCO is disabled and the EXTVCO, EXTVCO pair is enabled. That input pair is sine wave and PECL compatible.

The CPPOL pin sets the frequency slope polarity based on the operation of the external VCO. When CPPOL is low, the charge pump generates pulses for an integrator and loop filter assuming the VCO frequency goes lower as the integrator output voltage increases. When CPPOL is high, pulses are generated for a VCO in which the frequency goes higher as the integrator output voltage increases.

#### **Application Circuit**

A typical application circuit is shown in Figure 4. This drawing shows use of the internal reference oscillator and internal VCO.

Figure 4. Typical Application with Crystal Reference and Internal VCO

Arizona Microtek, Inc. reserves the right to change circuitry and specifications at any time without prior notice. Arizona Microtek, Inc. makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Arizona Microtek, Inc. assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Arizona Microtek, Inc. does not convey any license rights nor the rights of others. Arizona Microtek, Inc. products are not designed, intended or authorized for use as components in systems intended to support or sustain life, or for any other application in which the failure of the Arizona Microtek, Inc. product could create a situation where personal injury or death may occur. Should Buyer purchase or use Arizona Microtek, Inc. products for any such unintended or unauthorized application, Buyer shall indemnify and hold Arizona Microtek, Inc. and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Arizona Microtek, Inc. was negligent regarding the design or manufacture of the part.